|

|

〜 Main Menu 〜 ● コンテンツ ● サーバーについて ● ウェブログ ●外部リンク |

廉価FPGAでHDMI(DVI)出力・概要Altera の廉価 FPGA である Cyclone III を使って、 720p の HDMI(DVI) 信号を出力してみました。 DVI の電気的仕様では電流モード差動ドライバが必要ですが、通常の LVTTL IO と抵抗でエミュレートしています。  クリックで拡大 クリックで拡大

1.HDMI(DVI)の概要HDMI は DVI の拡張規格となっており、物理層と基本プロトコルは同じものです。サポートすべき映像フォーマットが異なるほか、 HDMI では映像以外のパケット(オーディオ等)が利用できます。 DVI では、最低限 640x480 の解像度と、24bit RGB フォーマットをサポートする必要があります。 HDMI ではこれに加え、 HDTV では 1280x720p または 1920x1080i をサポートする必要があります。 HDMI においては、色差信号(Y,CB,CR)や高階調(30,36,48bit)に対応することもできます(オプション)。 多くの DVI モニタや HDMI モニタで 720p が表示できるようです。 今回はこの 720p のモードを出力してみました。 720p では、ピクセルクロック 74.25MHz、データレート 742.5Mbps となります。

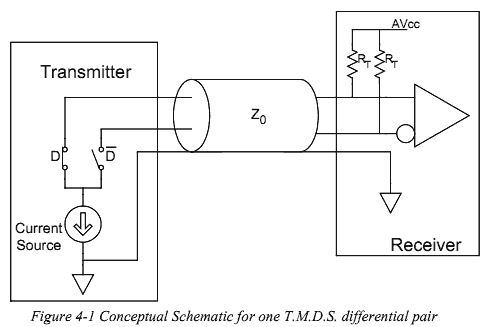

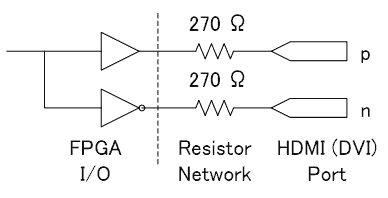

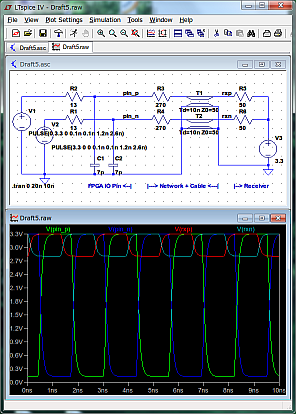

2.物理層の実装DVI 仕様書より電気的仕様を引用します。 終端抵抗 RT は 50Ω、終端電圧 AVcc は 3.3V、電流源は 10mA が標準値となっています。 50Ω に対して 10 mA 流れるので、オン時は 2.7V となります。 本稿では、この特性を以下のような簡単な回路で実現しています。  このときの FPGA I/O ピンの寄生素子を含めてシミュレーションを行った結果を以下に示します。  クリックで拡大 クリックで拡大実機では手持ち部品の関係で 200Ω の抵抗を使って駆動しています。

HDMI コネクタが用意できなかったので、 HDMI ケーブルをピンフレームで接続します。

HDMI ケーブルに至る間に2回ピンヘッダを通り、インピーダンスコントロールもされていないベーク基板でどれほどの信号品質が確保できるのでしょうか。

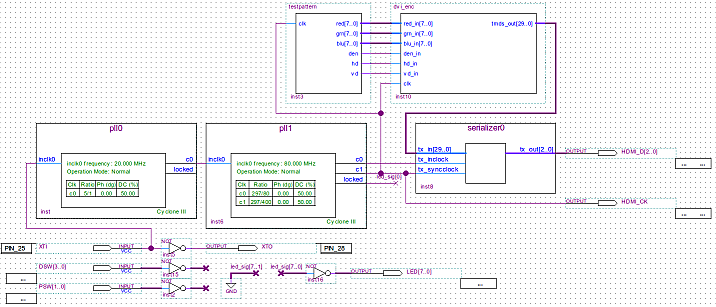

3.HDMI 信号の生成FPGA に実装したブロックは以下のようになっています。逓倍率の関係で、PLLを2段にしています。 また、使用している I/O 設定 LVDS_E_3R では 640Mbps までの制限があるので、 PLL の設定を変えてツールを騙しています。  クリックで拡大 クリックで拡大dvi_enc ブロックでは HDMI/DVI に使われている TMDS 信号のエンコードを行っています。 testpattern ブロックでは実際に表示する映像信号をデジタルRGBのフォーマットで生成しています。 Download

4.動作確認トップの画像や動画のように、乱れることなく映像出力ができています。複数のモニタで確認しましたが、映らなかったものはなかったので良好かと思います。 確認のため測定したデータ線のアイパターンを以下に示します。

|